Disposer d’un programme qui a fait ses preuves pour dialoguer avec un module via la ligne série I2C constitue une base solide pour exploiter les divers documents techniques disponibles sur la toile. On ne peut en faire l’économie. Pour ancrer les fondations de tout ce qui va suivre, un petit résumé sous forme d’une fiche me semble indispensable. Je ne peux que vous engager fortement à imprimer Synthétiseur H.F. 40MHz DSS AD9850 et garder ce petit « carton d’invitation » en permanence à portée de la main. Son schéma électronique de la Fig.2 et la photographie de la Fig.1 constitueront une aide précieuse à la compréhension des lignes de programme et à celle des résultats obtenus. En particulier la Fig.1 précise les divers branchements sur les connecteurs HE14.

Le programme démonstrateur P01.

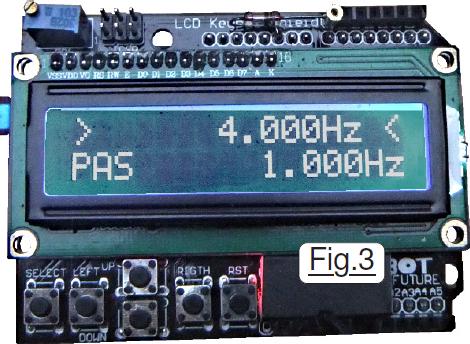

Conçu pour émuler un générateur entièrement autonome, il utilise le clavier local pour pouvoir programmer manuellement la fréquence du signal généré. La Fig.3 décrit l’affectation des cinq boutons poussoir du SHIELD. Trois sont dédiés à la consigne du PAS imposé, les deux autres provoquant des changements de fréquence en plus ou en moins.

Conçu pour émuler un générateur entièrement autonome, il utilise le clavier local pour pouvoir programmer manuellement la fréquence du signal généré. La Fig.3 décrit l’affectation des cinq boutons poussoir du SHIELD. Trois sont dédiés à la consigne du PAS imposé, les deux autres provoquant des changements de fréquence en plus ou en moins.

• BP SELECT : Le PAS est divisé par 10.

• BP LEFT : Le PAS est multiplié par 10.

• BP RIGHT : PAS = 1000 et fréquence = 1000.

• BP UP : La fréquence augmente du PAS.

• BP DOWN : La fréquence diminue du PAS.

Les options pour les valeurs du pas sont des multiples de 10. La fréquence de l’onde générée est limitée entre 1Hz et 40MHz. La notice indique que le circuit peut aller jusqu’à plus de 62MHz, mais j’ai estimé pour ma part que ne pas dépasser les 40MHz était raisonnable. En effet, mon récepteur radio « ondes courtes » servant au « contrôle qualité » talonne à cette fréquence maximale. De plus, l’oscilloscope utilisé pour visualiser les signaux ne permet pas d’observer au delà ce cette limite. Ne pouvant vérifier à des valeurs plus élevée, j’ai opté pour l’abstinence. Rien ne vous empêche du reste à changer cette limite dans le logiciel. Dans cette hypothèse, il n’y a que deux constantes à changer dans void loop().

Brancher, écouter, mesurer.

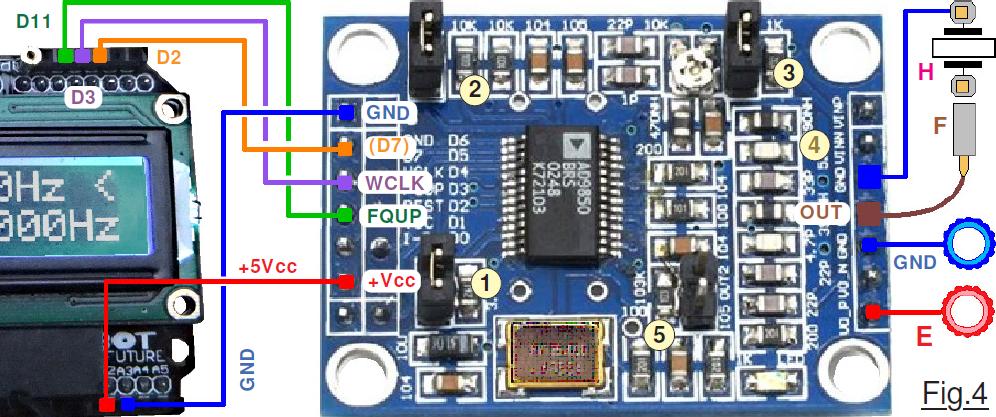

Programme P01_GENERATEUR_40MHz.ino téléversé sur Arduino, il importe de réaliser quelques liaisons filaires entre le SHIELD et le petit module électronique du synthétiseur de fréquences. La Fig.4 est représentative du câblage minimal à réaliser pour pouvoir effectuer les manipulations élémentaires et étudier la programmation de base pour dialoguer sur l’I2C. Passons en revue de détail ces divers branchements.

En premier lieu on récupère GND et le +5Vcc sur le SHIELD. Puis, nous établissons les trois lignes de dialogue série conformément aux choix exprimés dans le tableau proposé dans le chapitre précédent. C’est tout pour le connecteur série. D’après la documentation il faut mettre en place le « strap » 2 pour sélectionner le mode série par opposition au mode parallèle. Qu’il soit en place ou non, sur ma carte électronique je n’ai constaté aucune différence, c’est donc uniquement par « discipline » que ce pont est établi sur le petit connecteur HE14. Pour ces premier essais on laisse en place les « straps » 1 et 3, nous examinerons plus tard leurs finalités respectives. La sortie sinusoïdale OUT dont les harmoniques sont filtrées, délivre une onde d’amplitude 1V. Cette dernière est insuffisante pour permettre une mesure de la fréquence de ce signal au moyen de PICOLAB. On va donc utiliser un signal logique au format TTL sur la première broche du connecteur HE14 des sorties, sans oublier naturellement de réunir la masse GND. L’autre masse disponible va vers le petit haut-parleur H. Vous pouvez fort bien réunir le signal logique de la broche n°2 sur le BUZZER de PICOLAB. Mais personnellement je préfère un vrai dispositif acoustique qui reproduira proprement la tonalité « ronde » d’une onde sinusoïdale pure. Bien que la sortie OUT soit en basse impédance, y brancher le petit haut-parleur EKULIT de 8Ω dont il a déjà été question dans le didacticiel, diminue fortement l’amplitude du signal fourni. L’onde logique n’est alors plus correcte. Quand on désire mesurer la fréquence, il faut débrancher la petite fiche F. Enfin sachez que le signal logique ne sera effectif en E que si nous laissons la broche VINN en 4 non branchée. Les deux sorties passent à un état permanent si cette entrée est portée au niveau GND.

respectives. La sortie sinusoïdale OUT dont les harmoniques sont filtrées, délivre une onde d’amplitude 1V. Cette dernière est insuffisante pour permettre une mesure de la fréquence de ce signal au moyen de PICOLAB. On va donc utiliser un signal logique au format TTL sur la première broche du connecteur HE14 des sorties, sans oublier naturellement de réunir la masse GND. L’autre masse disponible va vers le petit haut-parleur H. Vous pouvez fort bien réunir le signal logique de la broche n°2 sur le BUZZER de PICOLAB. Mais personnellement je préfère un vrai dispositif acoustique qui reproduira proprement la tonalité « ronde » d’une onde sinusoïdale pure. Bien que la sortie OUT soit en basse impédance, y brancher le petit haut-parleur EKULIT de 8Ω dont il a déjà été question dans le didacticiel, diminue fortement l’amplitude du signal fourni. L’onde logique n’est alors plus correcte. Quand on désire mesurer la fréquence, il faut débrancher la petite fiche F. Enfin sachez que le signal logique ne sera effectif en E que si nous laissons la broche VINN en 4 non branchée. Les deux sorties passent à un état permanent si cette entrée est portée au niveau GND.

Signaux disponibles sur le module AD9850.

Branchements effectués, programme téléversé, nous pouvons commencer nos premières investigations. L’approche initiale consiste à cliquer sur les divers boutons du module LCD pour observer les affichages et s’habituer à leurs fonctions. S’entrainer pour rapidement être capable de programmer n’importe quelle fréquence dans la plage disponible. Imposez une fréquence de 3000Hz par exemple. Reliez la sortie F sur le BUZZER de PICOLAB. Le son est audible certes, mais du genre très discret. Pontez la ligne 4 et reliez le composant piézoélectrique sur l’une des deux sorties binaires. Cette fois la petite note timide

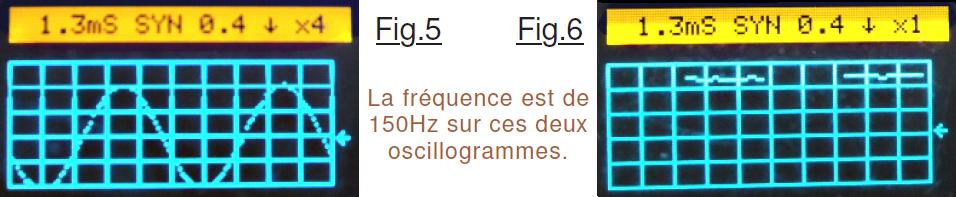

devient carrément pénible. Montez en fréquence, expérimentez la limite des ultrasons. Branchez un petit haut-parleur sur la sortie filtrée si vous en possédez un. Vous allez alors vous rendre compte que la note est plus douce. C’est la caractéristique d’une onde sinusoïdale, toute en « rondeur ». Quand vous en aurez assez de ces tonalités invasives, configurez PICOLAB en oscilloscope muni de tous ses modules d’exploitation. Débrancher le haut-parleur ainsi que la liaison 4. Fréquence ajustée à 150Hz nous obtenons le graphe de la Fig.5 qui montre une sinusoïde d’amplitude 1V dont la variation est comprise entre zéro et +1V. La Fig.6 pour sa part est significative des caractéristiques relatives aux signaux logiques lorsque le pont 4 est établi. La tension varie alors entre 0 et +4,5V et respecte les tensions représentatives de « 0 » et « 1 » du standard TTL.

devient carrément pénible. Montez en fréquence, expérimentez la limite des ultrasons. Branchez un petit haut-parleur sur la sortie filtrée si vous en possédez un. Vous allez alors vous rendre compte que la note est plus douce. C’est la caractéristique d’une onde sinusoïdale, toute en « rondeur ». Quand vous en aurez assez de ces tonalités invasives, configurez PICOLAB en oscilloscope muni de tous ses modules d’exploitation. Débrancher le haut-parleur ainsi que la liaison 4. Fréquence ajustée à 150Hz nous obtenons le graphe de la Fig.5 qui montre une sinusoïde d’amplitude 1V dont la variation est comprise entre zéro et +1V. La Fig.6 pour sa part est significative des caractéristiques relatives aux signaux logiques lorsque le pont 4 est établi. La tension varie alors entre 0 et +4,5V et respecte les tensions représentatives de « 0 » et « 1 » du standard TTL.

Les sinusoïdes de l’AD9850.

C’est pour se faire un petit plaisir que PICOLAB a été mis à contribution pour observer ces signaux, mais un travail sérieux pour évaluer le générateur impose des instruments de mesure autrement plus performants. Pour analyser la pureté des signaux sinusoïdaux, c’est un synchroscope HM705 qui a permis de faire les photographies qui suivent. C’est un fidèle serviteur qui totalise plus de trente années de bons et loyaux services. Loin d’égaler en performances les appareils actuels, sa bande passante de deux fois 20MHz permet déjà de se faire une idée précise de la qualité du circuit analysé. La belle forme de la Fig.7

est caractéristique de celle d’une onde pure, parfaitement sinusoïdale, donc sans présence d’harmoniques. Expérimentalement on obtient une telle propreté pour toute la plage de fréquences comprises entre 1Hz et 40MHz limite d’observation sur l’oscilloscope utilisé. L’amplitude est constante de 1V crête à crête entre 1Hz et 10MHz. Sur la Fig.8 le signal se « tasse » en largeur, car la base de temps la plus rapide sur l’appareil de mesures est de 0,05µS par graduation. La fréquence de

est caractéristique de celle d’une onde pure, parfaitement sinusoïdale, donc sans présence d’harmoniques. Expérimentalement on obtient une telle propreté pour toute la plage de fréquences comprises entre 1Hz et 40MHz limite d’observation sur l’oscilloscope utilisé. L’amplitude est constante de 1V crête à crête entre 1Hz et 10MHz. Sur la Fig.8 le signal se « tasse » en largeur, car la base de temps la plus rapide sur l’appareil de mesures est de 0,05µS par graduation. La fréquence de

l’onde observée est de 30MHz. L’amplitude observée a diminué, car le gain de l’oscilloscope à cette fréquence s’effondre. Constat identique sur la Fig.9 sur laquelle la forme du signal à 40MHz atteint les limites du raisonnable pour déduire des « vérités » fiables. Tous ces signaux ont été saisis sans précaution, c’est à dire uniquement par deux liaisons filaires volontairement bâclées, un peu longues et non blindées.

l’onde observée est de 30MHz. L’amplitude observée a diminué, car le gain de l’oscilloscope à cette fréquence s’effondre. Constat identique sur la Fig.9 sur laquelle la forme du signal à 40MHz atteint les limites du raisonnable pour déduire des « vérités » fiables. Tous ces signaux ont été saisis sans précaution, c’est à dire uniquement par deux liaisons filaires volontairement bâclées, un peu longues et non blindées.

L’agressivité des signaux logiques.

Autant une onde sinusoïdale sans harmoniques n’influence que peu l’environnement électromagnétique environnant, ne le perturbant que sur sa fréquence, autant un signal binaire crée des ravages en termes de pollutions radiofréquences. Ces tensions qui varient brutalement entre zéro et +5V puis retombent à zéro dans des durées de transitoire très courtes, présentent des harmoniques qui en théorie vont jusqu’à l’infini. Le générateur testé « annonce » des temps de commutation de 400V/µS, c’est à dire que le signal fourni peut passer de « 0 » à « 1 » TTL en moins de 0,013µS si on ne « ralenti pas la sortie » par des capacités parasites exagérées.

Pour illustrer la pollution en radiofréquences que peut générer un signal carré, observer la Fig.10 pour laquelle les deux voies de l’oscilloscope sont utilisées.

Normalement, tout technicien sérieux aurait utilisé pour chaque ligne un cordon blindé associé à une sonde à faible capacité parasite. C’est volontairement que j’ai caricaturé ce mesurage en reliant l’HM705 au circuit AD9850 par de simples fils électriques un peu longs. En B le signal carré présente une amplitude de 5V car il respecte le standard TTL. En A le gain est plus élevé, la sinusoïde présente une amplitude plus faible de 1Vcàc. Comme les lignes sont un peu longues, (Environ 30cm.) et surtout non blindées, elles font antenne. On voit que A est perturbé par B au point de capter les transitoires de commutation du signal TTL avec une amplitude de parasitage plus du double de celle de l’onde « utile ». En augmentant la fréquence des signaux générés par le synthétiseur, la Fig.11 en C et D devient caractéristique d’une auto-oscillation. Cette dernière résulte de la fréquence de résonance de la ligne relativement faible. Cette résonance à environ 80MHz résulte de la présence de capacité parasite « importante ».

Normalement, tout technicien sérieux aurait utilisé pour chaque ligne un cordon blindé associé à une sonde à faible capacité parasite. C’est volontairement que j’ai caricaturé ce mesurage en reliant l’HM705 au circuit AD9850 par de simples fils électriques un peu longs. En B le signal carré présente une amplitude de 5V car il respecte le standard TTL. En A le gain est plus élevé, la sinusoïde présente une amplitude plus faible de 1Vcàc. Comme les lignes sont un peu longues, (Environ 30cm.) et surtout non blindées, elles font antenne. On voit que A est perturbé par B au point de capter les transitoires de commutation du signal TTL avec une amplitude de parasitage plus du double de celle de l’onde « utile ». En augmentant la fréquence des signaux générés par le synthétiseur, la Fig.11 en C et D devient caractéristique d’une auto-oscillation. Cette dernière résulte de la fréquence de résonance de la ligne relativement faible. Cette résonance à environ 80MHz résulte de la présence de capacité parasite « importante ».

Générer du signal FSK avec le synthétiseur AD9850.

Anticipant le développement d’un générateur polyvalent aux possibilités étendues, nous allons tester la faculté de commutation rapide en fréquence qui caractérise le circuit intégré de notre application. On peut envisager en effet de créer plus tard une fonction de modulation par déplacement de fréquence, connue sous sa dénomination anglophone de Frequency-Shift Keying. Ce type de signal est très souvent employé, tout particulièrement dans le domaine

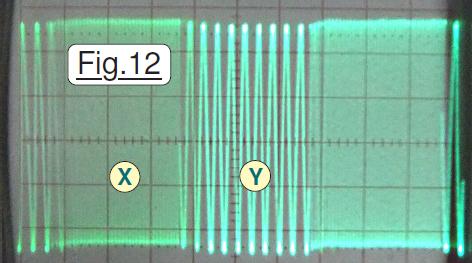

des MODEMs. Une première expérience consiste à téléverser P02_Generation_FSK_simple.ino qui fournit en boucle infinie deux tonalités qui alternent entre 5kHz et 20kHz. La Fig.12 a été obtenue avec un délai programmé de 1mS pour chaque tonalité. On distingue parfaitement la zone X à 20kHz et celle Y à 5kHz. Cette photographie a été obtenue « à la volée », car le graphe se décale latéralement en permanence et rapidement car chaque alternance montante déclenche la base de temps. Pour que l’image puisse être stable, il faut la synchroniser sur l’instant des changements de fréquence et non sur le signal généré. D’où l’idée de fournir un signal externe de synchronisation chaque fois que le programme commute la fréquence.

des MODEMs. Une première expérience consiste à téléverser P02_Generation_FSK_simple.ino qui fournit en boucle infinie deux tonalités qui alternent entre 5kHz et 20kHz. La Fig.12 a été obtenue avec un délai programmé de 1mS pour chaque tonalité. On distingue parfaitement la zone X à 20kHz et celle Y à 5kHz. Cette photographie a été obtenue « à la volée », car le graphe se décale latéralement en permanence et rapidement car chaque alternance montante déclenche la base de temps. Pour que l’image puisse être stable, il faut la synchroniser sur l’instant des changements de fréquence et non sur le signal généré. D’où l’idée de fournir un signal externe de synchronisation chaque fois que le programme commute la fréquence.

Fournir un signal de synchronisation externe reste très simple informatiquement. C’est du reste ce qui a été fait pour le petit oscilloscope numérique de PICOLAB. Dans la boucle de base on inverse l’état logique d’une sortie à son début par exemple, et le tour est joué.

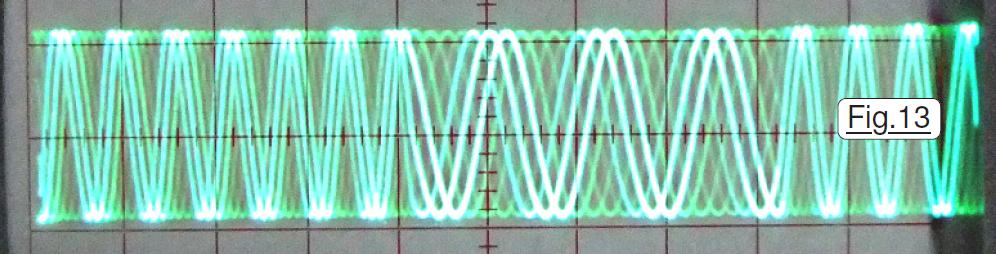

Comme la sortie binaire D12 est disponible, c’est tout naturellement que P03_Generation_FSK_avec_SYNext.ino va générer un signal de synchronisation sur cette dernière. Bénéficiant de cette possibilité de déclencher le balayage à chaque changement de tonalité, on peut s’attendre à un graphe univoque sur l’écran de l’oscilloscope. Déception : La Fig.13 démontre à l’évidence que les zones de commutation sont stables latéralement sur l’écran gradué, par contre, à l’intérieur des ces dernières les alternances du signal synthétisés sont fluctuantes. La fiche de caractéristiques en donne l’explication : La commutation des fréquences peut se faire très rapidement, mais elle est asynchrone, c’est à dire qu’elle se produit à un moment quelconque de la période du signal.

>>> SYNext n’est donc pas d’un grand intérêt. Il sera donc inutile sur le plan pratique de prévoir un tel signal électrique.

ANALYSE des procédures de pilotage de la ligne I2C.

Croiser les informations des documents techniques avec certaines lignes du programme démonstrateur P01_GENERATEUR_40MHz.ino va nous permettre de comprendre les instructions à fournir sur la ligne de dialogue entre Arduino et le synthétiseur de fréquences. Les signaux à imposer sur la liaison I2C sont tellement simples à générer qu’il est totalement inutile de rechercher une quelconque bibliothèque sur l’Internet. Ce chapitre va nous octroyer une totale autonomie pour développer un projet de générateur H.F. polyvalent.

Un tantinet de logique.

S’informer dans les notices de caractéristiques et d’application relève du pléonasme. C’est la première action à conduire avant toute tentative de mise en service d’un composant électronique quelconque. La lecture des documents techniques de l’AD9850 a conduit à la réalisation de la fiche dédiée Synthétiseur H.F. 40MHz DSS AD9850 qui en résume les différents connecteurs. Il reste à formaliser les signaux à appliquer sur les trois broches pilotant la ligne I2C. Examinons ensemble la logique de fonctionnement de notre circuit intégré complexe, qui consiste à faire passer un éléphant de 32 BITs dans une ligne ne

pouvant présenter que deux états logiques « 0 » et « 1 ». À ces quatre OCTETs définissant la valeur de la fréquence à générer, il faut ajouter un octet de plus pour préciser au circuit intégré la nature de l’information qui vient d’être transmise en ligne série I2C.

pouvant présenter que deux états logiques « 0 » et « 1 ». À ces quatre OCTETs définissant la valeur de la fréquence à générer, il faut ajouter un octet de plus pour préciser au circuit intégré la nature de l’information qui vient d’être transmise en ligne série I2C.

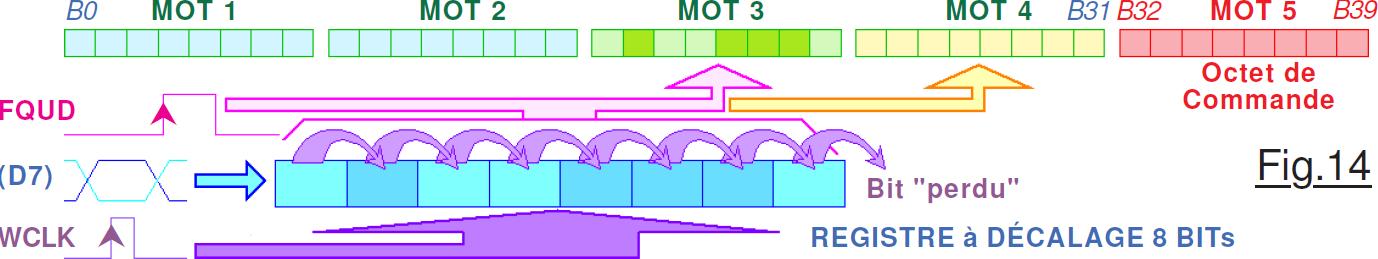

Le principe du transfert dans sa globalité est représenté sur la Fig.14 qui montre que le registre à décalage du récepteur série de la ligne I2C ne fait que huit BITs.

Fonctionnement du registre à décalage.

Toute mémorisation d’une suite de BITs fugitifs qui transitent sur une ligne série consiste à sauvegarder l’état momentané dans des cellules mémoires du type registre « parallèle ». On retrouve à chaque fois un inévitable registre à décalage représenté sur la Fig.14 en bleu. Le principe de fonctionnement du circuit AD9850 est très banal. Examinons la nature des signaux attendus :

• On place sur la ligne des données (D7) un état « 0 » ou un état « 1« .

• Quand la tension est stabilisée sur la ligne (D7), on fait passer à l’état « 1 » la ligne de signal d’horloge WCLK puis on la fait revenir à « 0 ». Le front montant déclenche un décalage « à droite » dans le registre de conversion SÉRIE vers PARALLÈLE. Tous les BITs de cet OCTET sont décalés d’une position. Celui de droite est « perdu ». Le BIT de gauche prend l’état présent sur (D7).

• On recommence huit fois l’opération précédente, mais pas plus car ensuite des BITs seraient perdus.

Une phrase à cinq mots.

Dialoguer devient un monologue dans notre cas, car la ligne I2C ne fait que parler, elle fonctionne en aveugle et n’attend pas de retour par l’entité qui « écoute » sur une ligne dédiée. C’est exactement ce que fait une horloge parlante, ou un poste récepteur de radio. Ils parlent avec des phrases dans une langue préétablie, peu importe si « de l’autre coté du fil » il y a quelqu’un pour écouter. Arduino va fonctionner exactement de la même façon. La ligne I2C va transmettre une information codée avec un protocole défini par le concepteur du circuit intégré. Si on respecte ce protocole, le circuit AD9850 comprendra la consigne et réalisera avec discipline cette dernière. Examinons en détail le protocole prévu pour imposer une donnée au synthétiseur :

La phrase complète s’articule sur une suite de cinq mots de huit bits chacun, soit un total de 40 BITs. Les quatre premiers mots définissent la valeur de la fréquence exprimée en binaire sur 32 BITs numérotés de 0 à 31. Comme il faut décharger le registre à décalage chaque fois qu’il est saturé, c’est à dire qu’il a mémorisé huit BITs, (Donc un mot du protocole.) une ligne de commande doit informer la logique de contrôle. Dans notre cas c’est le front montant de la ligne FQUD qui provoque le transfert du registre à décalage vers les mots de données. Sur un RESET de l’AD9850 un pointeur est indexé sur le MOT 1. Le front montant sur la ligne FQUD provoque deux actions. La première consiste à recopier les huit BITs du registre à décalage vers le mot indexé. La deuxième action consiste à incrémenter le pointeur pour indexer le mot suivant. (Ou revenir sur le premier.)

Récupérer une donnée complète sur la ligne I2C consiste donc à mémoriser les cinq mots.

Écouter, comprendre, agir …

Partie intégrante du protocole à respecter, la logique du circuit synthétiseur de fréquence compte les fronts montants arrivant sur la ligne FQUD. Arrivé à la valeur critique de cinq, le système considère qu’une donnée est entièrement présente sur les 40 BITs qu’il importe de la traiter.

C’est le mot de contrôle MOT 5 qui contient la consigne définissant l’action à exécuter. La composition de cette information est la suivante :

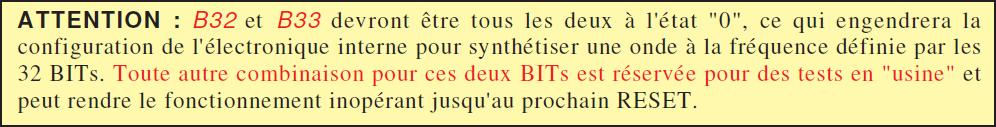

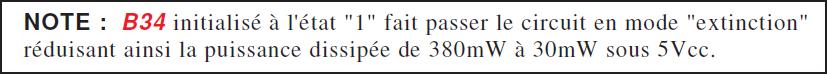

• B32 et B33 sont des BITs de contrôle. (Toujours les forcer à « 0 ».)

• B34 à l’état « 1 » passe le circuit en mode veille, les sorties restent à zéro volt.

• B35 et B36 sont des BITs définissant le déphasage entre signal d’horloge interne et les signaux synthétisés. Il est ainsi possible en utilisant deux circuits AD9850, de générer des ondes dont on peut à convenance décaler la phase. Dans ce cas ces deux circuits doivent utiliser une horloge commune externe sur la broche 9 nommée RFCLOCKI. Nous ne sommes pas concernés par cette possibilité, ces cinq bits seront ignorés, on pourra par exemple les forcer à « 0 ».

Signaux à fournir sur la liaison série I2C.

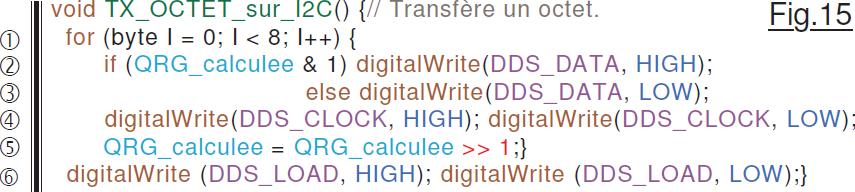

Engendrer la production d’une onde dont on peut avec rigueur imposer la fréquence va s’avérer très simple. Il suffit avec Arduino de générer cinq fois la transmission d’un mot de huit BITs. Chaque mot sera géré en plaçant sur (D7) l’état désiré, en créant une impulsion d’horloge sur la ligne WCLK. Quand les huit BITs sont transférés dans le registre à décalage, on provoque un front montant sur FQUD que l’on replace immédiatement à zéro pour préparer la transmission du mot suivant. Dans le programme P01_GENERATEUR_40MHz.ino la procédure suivante est chargée de ce travail en puisant ses huit BITS dans ceux de la variable QRG_calculee.

La ligne (1) impose de faire huit fois.

En (2) et (3) on force la ligne (D7) à « 1 » ou « 0 » en fonction de l’état du BIT n°0 de QRG_calculee.

Le code (4) génère un front montant puis une remise à l’état « 0 » de la ligne WCLK.

En (5) on décale d’une position à droite le contenu de QRG_calculee pour préparer le bit suivant.

Enfin (6) entérine l’octet en générant le front montant sur FQUD puis replace la ligne à « 0 ».

La logique du circuit synthétiseur de fréquence est extrêmement rapide et réagit en quelques nanosecondes. Il n’est donc pas du tout nécessaire de prévoir des temporisations, on peut faire travailler l’ATmega328 au maximum des ses possibilités. Maintenant que nous possédons une procédure pour transmettre puis transférer un mot dans l’AD9850, voyons comment gérer un quintuplé qui permettra d’imposer à notre guise la fréquence du signal fourni.

« Causer » en cinq mots.

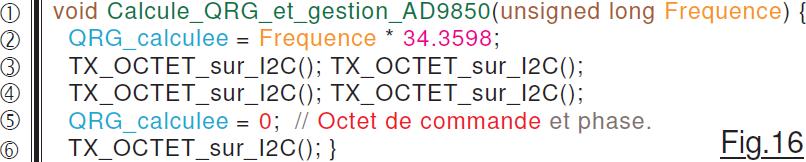

Émuler une séquence de dialogue entière n’exige en C++ de l’IDE que sept instructions, autant dire pas grand chose. L’intégralité du code se résume au listage de la Fig.16 qui démontre que l’on peut aisément se passer d’une quelconque bibliothèque spécialisée. Examinons ligne à ligne le déroulement du processus. On remarque immédiatement que l’on va bien transmettre cinq mots car il est fait appel cinq fois à la procédure TX_OCTET_sur_I2C().

En ligne (1) la procédure reçoit en paramètre dans Frequence la valeur de la fréquence à générer. Par exemple l’appel sera du type : Calcule_QRG_et_gestion_AD9850(1000); si l’on désire que la fréquence des signaux soit de 1000Hz.

L’instruction (2) transforme dans la variable QRG_calculee cette valeur en binaire. La valeur du coefficient multiplicateur 34.3598 est étudiée dans le chapitre qui suit. La variable QRG_calculee est de type unsigned long et contient en binaire la valeur de la fréquence à générer codée sur 32 BITs. Les lignes (3) et (4) font quatre fois appel à la transmission de huit BITs. Chaque fois c’est la variable globale QRG_calculee qui est décalée d’une position à droite. On transmet donc par l’entremise de ces deux lignes de code l’intégralité du paramètre Frequence.

En (5) on place dans QRG_calculee la valeur de l’Octet de commande. (Valeur imposée : zéro.)

Un dernier appel en (6) à TX_OCTET_sur_I2C() transmet sur la ligne I2C le dernier MOT 5 du protocole qui déclenche l’action dans le circuit intégré du synthétiseur.

Les Fig.15 et Fig.16 présentent l’intégralité des procédures de servitudes qui permettent de mettre en œuvre l’AD9850, avouez que ce circuit est très facile à utiliser. Il nous reste toutefois à comprendre ce mystérieux coefficient de valeur 34.3598. Pour le codage de l’Octet de commande. On a simplifié au maximum en tenant compte de l’information donnée dans l’encadré jaune donné ci-avant. B32 et B33 sont à « 0 » pour imposer un changement de fréquence, B34 est à l’état « 0 » pour ne pas imposer le mode veille. Enfin, comme la valeur du déphasage peut être quelconque puisque nous ne nous en servons pas, autant donner des « 0 » pour les cinq BITs, ainsi l’Octet de commande vaut zéro.

Coder la valeur de la fréquence en binaire.

Forcément, la façon de coder les 32 BITs relève de la prise en compte des documents techniques dédiés au circuit intégré mis en application dans le projet. En consultant les informations disponibles, on déduit en particulier la formule pratique suivante :

![]()

Dans cette équation, le résultat correspond à la fréquence exprimée en Hz du signal qui sera généré, (À condition que le circuit ne soit pas mis en Extinction.) lorsque le paramètre Frequence est lui même exprimé en Hz. Le paramètre CLKref représente la fréquence, toujours exprimée en Hz, du signal d’horloge appliqué sur la broche n°9 nommée RFCLOCKI, laissant au concepteur la possibilité d’y brancher la sortie d’un oscillateur de son choix. Le concepteur du petit module utilisé dans ce projet a opté pour un oscillateur intégré de 125MHz. Donc, dans notre cas la formule devient :

Fréquence du signal = Frequence * 2 (puissance 32) / 125000000

Utilisée sous cette forme, le codage en C++ pourrait être le suivant :

unsigned long QRG_calculee = (Frequence * pow(2, 32)) / 125000000;

Introduite comme tel dans le programme, cette ligne de code convient parfaitement pour générer le signal attendu. En termes d’élégance de programmation, on ne peut pas en dire autant, car on impose au microcontrôleur une foule de calculs inutiles, et par voie de conséquences une taille de programme exagérée et des temps de traitement inutilement longs. Par exemple, la valeur de 2 (puissance 32) est une constante qui vaut 4294967295, autant la faire calculer une fois pour toute par le compilateur. Le codage en C++ devient :

unsigned long QRG_calculee = (Frequence * 4294967295) / 125000000;

Ceci étant précisé, diviser une constante par une constante donne encore une constante. Alors autant effectuer ce calcul à l’avance et en soumettre directement le résultat au compilateur.

4294967295 / 125000000 = 34,35973836. La ligne de programme devient :

unsigned long QRG_calculee = Frequence * 34,35973836;

Correction logicielle de la fréquence de référence.

Éternel recommencement, tout appareil de mesure étant constitué de composants imparfaits, il faut en peaufiner le plus finement possible les ajustements matériels ou logiciels disponibles. Dans notre cas, le cœur du système est constitué par l’oscillateur intégré. Ce dernier est enfermé dans un boitier métallique pour éviter qu’il ne rayonne à tout va, petite cage de Faraday sur laquelle est gravé la valeur de 125.000 annonçant la fréquence théorique de 125,000MHz. La réalité est un tantinet moins mathématique. La fréquence réelle sera calibrée par un quartz interne qui forcément s’écarte très légèrement de cette valeur, étant issu d’un processus industriel victime obligatoirement d’une petite dispersion de caractéristiques. Par ailleurs, ce minuscule morceau de « caillou » vibrera en fonction de ses dimensions réelles, ces dernières se modifiant en fonction de la température de ce matériau piézoélectrique. (Dilatation thermique de tout matériau « banal ».)

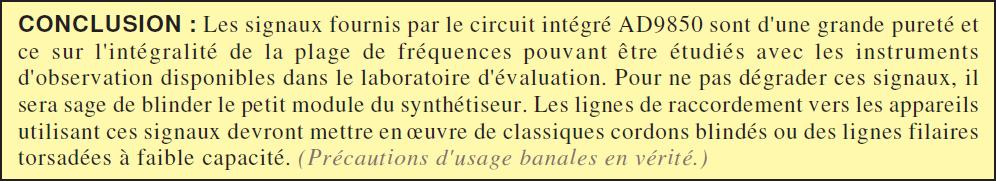

CONCLUSIONS :

• Ne pouvant modifier les dimensions mécaniques du quartz, on ne peut agir que par logiciel.

• Il suffit de corriger légèrement la valeur 34,35973836 pour l’adapter à la fréquence réelle de l’oscillateur. Pour ce faire, on comparera la fréquence réelle

x générée par le synthétiseur à une fréquence la plus élevée possible, avec un étalon fiable.

x (Les balises de fréquences sur ondes courtes sont précisément faites pour ça !)

• On ne procèdera à cet ajustement logiciel de paramètre que lorsque tous les appareils mis en service lors de cette manipulation seront à température

x stabilisée. Par exemple on effectue le contrôle lorsque le synthétiseur est sous tension depuis au moins une demi-heure.

La correction logicielle :

Plusieurs moyens sont utilisables, pour ma part j’en ai utilisé deux qui sont à la fois disponibles et fiables. Le premier consiste à utiliser un fréquencemètre local piloté par une horloge à quartz thermostatée, elle même calibrée sur des balises « ondes-courtes ». Cette mesure est fiabilisée après une mise en fonctionnement de plus d’une heure. La plus grande fréquence mesurable sur cet appareil se situe entre 25MHz et 30MHz. La fréquence réelle générée est sur le prototype plus importante que celle consignée. Il faut donc multiplier 34,35973836 par un coefficient légèrement supérieur à 1 et proportionnel à l’écart constaté. Suite à de nombreux essais, sur le prototype ce coefficient est évalué à la valeur de 1,0000018 qu’il faut introduire dans nos calculs.

unsigned long QRG_calculee = Frequence * 34,35973836 * 1.0000018;

Ce coefficient montre que la fréquence de référence une fois stabilisée avoisine 125000225MHz avec un écart par rapport à la valeur inscrite sur le boitier faible mais qui impose néanmoins une correction. Vous avez compris que l’on effectue le calcul « à la main », et que dans le programme seule la constante qui en résulte sera codée :

unsigned long QRG_calculee = Frequence * 34,3598;

Évaluation des performances et faisabilité.

Disposant des deux procédures de servitude qui nous permettent à convenance d’imposer une fréquence aux signaux générés par le synthétiseur, nous allons pouvoir développer un projet plus étoffé, visant à concevoir un générateur polyvalent couvrant tous les besoins dont on peut formuler la liste « actuellement » ; sachant que par la suite il sera toujours possible d’ajouter à notre guise de nouvelles fonctions. Cependant, il serait imprudent de se précipiter dans la programmation sans avoir une idée précise des performances de l’AD9850 et d’évaluer ce qui sera possible. Ce n’est qu’après avoir sérieusement effectué cette étude préalable que l’on pourra envisager l’agencement matériel qui forcément sera tributaire des exigences en Entrées/Sorties.

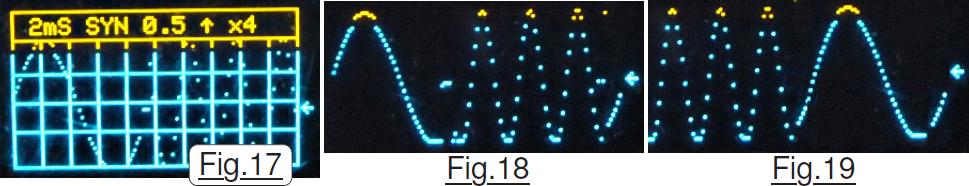

Fournir la belle Fig.13 image bien le propos, mais ne pas expérimenter cette manipulation réellement est un peu frustrant, d’autant plus que l’on dispose d’un oscilloscope réputé expérimental. Le programme élémentaire P04_FSK_pour_PICOLAB.ino permet de combler cette lacune. Quand il est activé, les paramètres étant ceux de la Fig.17, on constate effectivement que chaque balayage se décale par rapport aux sinusoïdes générées. Remarquez que c’est normal, car PICOLAB n’a pas été prévu pour être déclenché par un signal externe, donc mobiliser une sortie de l’ATmega328 pour générer une SYNEXT ne sera raisonnable que si des sorties binaires restent inutilisées quand toutes les broches auront été assignées ce qui reste à démontrer.

Fonctionnant à la plus grande rapidité possible, la boucle de base du petit démonstrateur P05_FSK_rapide.ino s’utilise en deux étapes. La première consiste à le téléverser et à brancher PICOLAB sur la sortie de SYNEXT. La fonction IMPULSIOMÈTRE montre que l’impulsion de synchronisation exige environ 5µS. Pour calculer les délais imposés pour changer la valeur de la fréquence, on divise la durée à l’état « 0 » par deux ce qui fait environ 1790µS / 2 soit 895µS. Ce calcul n’est toutefois pas rigoureux, car il ne tient pas compte du temps exigé par le programme pour « reboucler » dans void loop. Pour la deuxième étape, on passe en remarque les deux lignes imposant la valeur de la fréquence. Il ne reste plus que le bouclage dans void loop et la génération de SYNEXT. La période de la boucle de base devient 10µS. On peut donc en déduire que :

![]()

Surtout n’imaginez-pas que ce test n’est qu’une manipulation pour faire du « remplissage ». C’est la connaissance de cette information qui d’emblée détermine la limite de rapidité de changement de fréquence sur le synthétiseur. Cette limitation n’est pas le fait du circuit AD9850 qui peut commuter en environ 0,05µS mais de la « lenteur relative » de fonctionnement du microcontrôleur ATmega328 associé à du code binaire généré par le compilateur de l’IDE.

Nous disposons de tous les éléments théoriques pour pouvoir avec des chances raisonnables de succès, commencer à développer un projet élaboré digne de ce nom. Jusqu’à présent les démonstrateurs faisaient appel au SHIELD LCD, il est temps de commencer à investir pour le plus long terme, c’est à dire orienter les programmes vers l’utilisation de l’afficheur graphique OLED. Reste que parmi vous, beaucoup n’ont aucune intension d’investir dans le SHIELD LCD, aussi pour vous éviter d’avoir à transposer ces cinq premier programmes, je vous propose les équivalents qui anticipent un peu sur la version définitive car ils respectent déjà la répartition des Entrées / Sorties qui sera affectée au prototype de développement.

Vous avez bien compris que ces programmes vont du démonstrateur P06 au logiciel P10.

Les cheminements sérieux vont pouvoir commencer …

Bonjour et félicitations pour votre travail auquel je me réfère à maintes reprises.

Très intéressé par votre Générateur_40MHz (PO6 version afficheur OLED) je ne trouve pas le shéma (et éventuellement le tracé du circuit imprimé).

Comment puis-je le(s) télécharger ? (ou pouvez-vous me le(s) faire parvenir)

Merci d’avance.